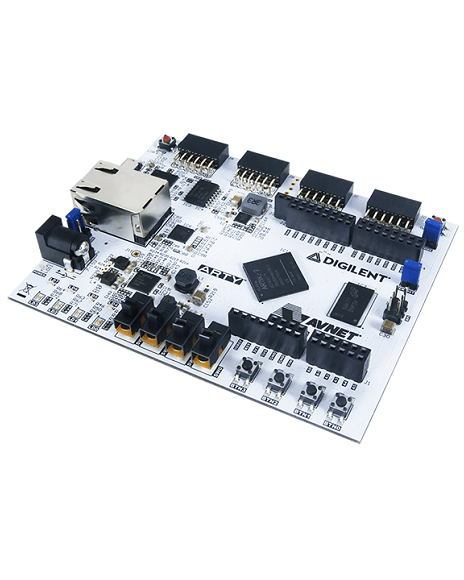

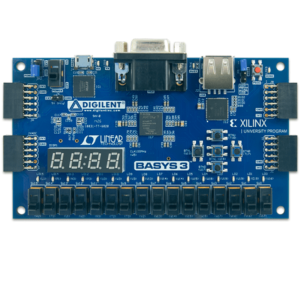

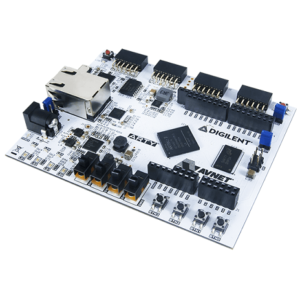

La Arty es una plataforma de desarrollo diseñada alrededor de la FPGA Artix-7 de Xilinx.

La FPGA se caracteriza por:

Tiene 33280 celdas lógicas en 5200 slices, la cual cada slice tiene 4 LUTs (tablas de búsqueda) de 6 entradas, y 8 flip-flops.

Rápido bloque RAM de 18MBits.

Posee 5 CMT (clock management tiles), cada uno con PLL (phase-locked loop).

Tiene 90 DSP slices.

La velocidad del reloj interno excede 450MHz.

Tiene integrado un conversor análogo a digital (XADC).

Es programable por JTAG y Flash Quad-SPI.

El sistema se caracteriza por:

DDR3 de 256MB con 16 bits a 667MHz.

Flash Quad-SPI de 16MB.

Circuito de programación USB-JTAG (requiere cable micro USB, no incluido).

La fuente de alimentación puede ser por USB o cualquier fuente desde 7V hasta 15V.

El sistema de conexión es Ethernet de 10/100Mbps, USB-UART bridge.

Posee 4 interruptores, 4 botones, un botón de Reset, 4 LED, 4 LED RGB.

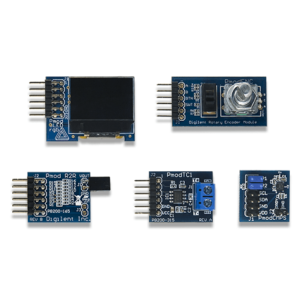

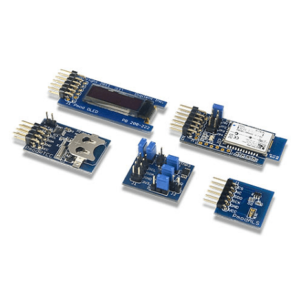

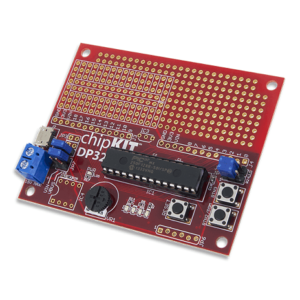

Tiene 4 conectores Pmod, y conector para Shield de Arduino/chipKIT.

Documento: